Friday, February 08, 2013

試作チップ36(65nm)

原田

LEAP

LPT4S

SC16

試作チップ35(65nm)

LEAP

LPT-4S

SC08

試作チップ34(65nm)

大政

VDEC

2012/10/10 TO

試作チップ33(65nm)

原田

LEAP

LPT-3

試作チップ32(65nm)

天木、原田

TED

2012/8 TO

試作チップ31(180nm)

Igors

2012/7/25 TO

試作チップ30(65nm)

Dawood, 郡浦

VDEC

2012/4/4 TO

試作チップ29(65nm)

Dawood, 郡浦

VDEC

2012/2/22 TO

試作チップ28(65nm)

プロセス: 65nm CMOS 12層配線プロセス (VDEC)

チップサイズ: 2mmx2mm

トランジスタ数: ????

ゲート数: ????

設計者: 天木君、橋本

テープアウト: 2011/11/20

題目:耐環境変動オシレータベース真性乱数生成回路の試作2

オシレータサンプリング方式真性乱数生成回路の環境変動に対する耐性を高めるためには、高速オシレータのデューティ比を自律的に調整することが有効と考えられる。また、インジェクションロッキングを利用した乱数生成回路への攻撃方法が提案されており、攻撃によるゆらぎ量低下への対応が要求されている。本試作では、デューティ比モニタおよびデューティ比調整回路から構成される、デューティ比自動調整機構を実装した。また、オシレータに対するインジェクションロッキング攻撃の評価を行うため、NAND列を用いた電源ノイズ発生源および電源ノイズ測定回路を実装した。さらに、ゆらぎ量低下を検知するためのゆらぎモニタを実装した。提案するデューティ比自動調整機構により、温度を 5 ~ 60 [℃]と変化させた場合の `1' 出現確率変動量を 0.90 [%] から 0.05 [%]に低減できることを確認した。これは、NIST Frequency test に合格するのに十分な低減効果である。また、デューティ比モニタは、ランダムサンプリング法を用いたデューティ比推定方法と比較して 3,500 倍高速にデューティ比を推定可能であることを確認した。さらに、電源ノイズ発生源を用いた評価から、印加する電源ノイズの周波数とオシレータの周波数が近いとき、ゆらぎ量が低下することを確認した。

チップサイズ: 2mmx2mm

トランジスタ数: ????

ゲート数: ????

設計者: 天木君、橋本

テープアウト: 2011/11/20

題目:耐環境変動オシレータベース真性乱数生成回路の試作2

オシレータサンプリング方式真性乱数生成回路の環境変動に対する耐性を高めるためには、高速オシレータのデューティ比を自律的に調整することが有効と考えられる。また、インジェクションロッキングを利用した乱数生成回路への攻撃方法が提案されており、攻撃によるゆらぎ量低下への対応が要求されている。本試作では、デューティ比モニタおよびデューティ比調整回路から構成される、デューティ比自動調整機構を実装した。また、オシレータに対するインジェクションロッキング攻撃の評価を行うため、NAND列を用いた電源ノイズ発生源および電源ノイズ測定回路を実装した。さらに、ゆらぎ量低下を検知するためのゆらぎモニタを実装した。提案するデューティ比自動調整機構により、温度を 5 ~ 60 [℃]と変化させた場合の `1' 出現確率変動量を 0.90 [%] から 0.05 [%]に低減できることを確認した。これは、NIST Frequency test に合格するのに十分な低減効果である。また、デューティ比モニタは、ランダムサンプリング法を用いたデューティ比推定方法と比較して 3,500 倍高速にデューティ比を推定可能であることを確認した。さらに、電源ノイズ発生源を用いた評価から、印加する電源ノイズの周波数とオシレータの周波数が近いとき、ゆらぎ量が低下することを確認した。

試作チップ27(180nm)

信田

2011/11/18 TO

試作チップ26(180nm)

Igors

2011/7/27 TO

試作チップ25(65nm)

プロセス: 65nm CMOS 12層配線プロセス

チップサイズ: 2mmx2mm

トランジスタ数: ????

ゲート数: ????

設計担当者: 天木君、原田君、橋本

テープアウト: 2011/4

題目(天木分):耐環境変動オシレータベース真性乱数生成回路の試作1

オシレータサンプリング方式真性乱数生成回路においては、低速オシレータのゆらぎ量を大きくすることと、高速オシレータのデューティ比を適切な値に設定することが重要である。本試作では、負荷を利用したゆらぎ増幅回路とゆらぎモニタ回路、デューティ比モニタ回路とデューティ比調整回路を実装した。ゆらぎ増幅回路においては、25 ℃において 2.2 倍のゆらぎ利得を達成した。また、デューティ比調整回路により、44.3 ~ 45.7 [%]の範囲で、約 0.2 [%]の解像度でデューティ比を調整できることを確認した。また、ゆらぎモニタ回路においては、オシレータのゆらぎ量が小さい場合に自動的に分周を行う動作を確認した。一方、デューティ比モニタ回路については、設計上の論理的なミスにより、動作を確認することができなかった。

試作チップ24(180nm)

Igors

2010/10/18 TO

試作チップ23(65nm)

原田

TED

2010/10/6 TO

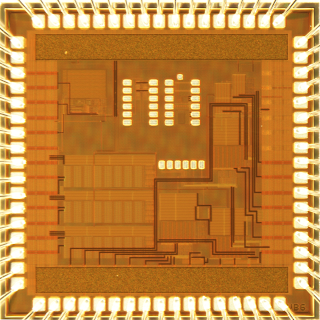

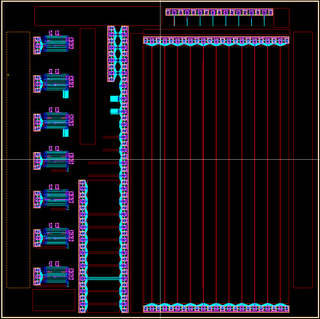

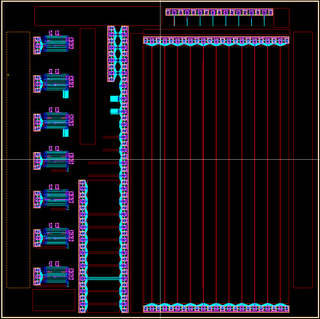

試作チップ22(65nm)

物理乱数生成器

プロセス: 65nm CMOS 12層配線プロセス

チップサイズ: 2mmx2mm

トランジスタ数: ????

ゲート数: ????

設計者: 天木君、高井君、橋本

テープアウト: 2010/8/24

チップ題目: 周期ゆらぎ増幅回路とデューティ比調整回路の試作

概要:オシレータサンプリング方式乱数生成回路は, 回路の内部雑音に起因するランダムな周期ゆらぎを利用して予測不可能な乱数を生成する回路であ

る. しかし, 出力の統計的ランダム性が低いため, ビットに対して後処理を行うことが一般的であり, そのために面積・電力コストが増大している. 高品質

の乱数を得るためには, オシレータの周期ゆらぎ量を大きくすること, また, オシレータのデューティ比を精密に調整することが必要である. そこで本試作

では, 速度制御可能バッファを用いてゆらぎを増幅する回路, およびプログラマブルバッファを用いてデューティ比を詳細に調整する回路を実装した. デュ

ーティ比調整回路の測定結果より, 7段リングオシレータのデューティ比が, 49.81~50.69 [%] の範囲で0.22 [%]の精度で調整可能であり, 乱数テスト

合格に必要な性能を満足していることを確認した. 一方, ゆらぎ増幅回路では, 今回用いた速度切り替え法が想定よりも長いレイテンシとなったため, 別の

切り替え法を用いた実装での増幅率に達しなかった.

プロセス: 65nm CMOS 12層配線プロセス

チップサイズ: 2mmx2mm

トランジスタ数: ????

ゲート数: ????

設計者: 天木君、高井君、橋本

テープアウト: 2010/8/24

チップ題目: 周期ゆらぎ増幅回路とデューティ比調整回路の試作

概要:オシレータサンプリング方式乱数生成回路は, 回路の内部雑音に起因するランダムな周期ゆらぎを利用して予測不可能な乱数を生成する回路であ

る. しかし, 出力の統計的ランダム性が低いため, ビットに対して後処理を行うことが一般的であり, そのために面積・電力コストが増大している. 高品質

の乱数を得るためには, オシレータの周期ゆらぎ量を大きくすること, また, オシレータのデューティ比を精密に調整することが必要である. そこで本試作

では, 速度制御可能バッファを用いてゆらぎを増幅する回路, およびプログラマブルバッファを用いてデューティ比を詳細に調整する回路を実装した. デュ

ーティ比調整回路の測定結果より, 7段リングオシレータのデューティ比が, 49.81~50.69 [%] の範囲で0.22 [%]の精度で調整可能であり, 乱数テスト

合格に必要な性能を満足していることを確認した. 一方, ゆらぎ増幅回路では, 今回用いた速度切り替え法が想定よりも長いレイテンシとなったため, 別の

切り替え法を用いた実装での増幅率に達しなかった.

試作チップ21(65nm)

放射線起因一過性パルス(SET) パルス幅測定回路

プロセス: 65nm CMOS 12層配線プロセス

チップサイズ: 2mmx2mm

トランジスタ数: 1,196k

ゲート数: 299k

設計者: 原田君、橋本

テープアウト: 2010/8

チップ題目: 放射線起因一過性パルス(SET) パルス幅測定回路の改善版試作

概要: 本試作では,試作チップ18の放射線起因一過性パルス(SET)のパルス幅測定回路を改善し,製造ばらつきや負バイアス温度不安定性(NBTI)によるパルス幅変動の除去と高いSETターゲット面積効率の実現を目的とした.試作回路では,10段のインバータチェインを並列化したものを1個のパルス幅測定回路に収束することで,高いターゲット回路面積を実現した.また,SETの伝播経路によるパルス幅の変動を校正するための校正機構を実装した.試作チップを用いて中性子照射実験を実施し,SETのパルス幅分布を取得可能であることを確認した.また,回路の校正によりチップ間/チップ内製造ばらつきがパルス幅測定にとって無視できないものであることを確認した.

Friday, April 02, 2010

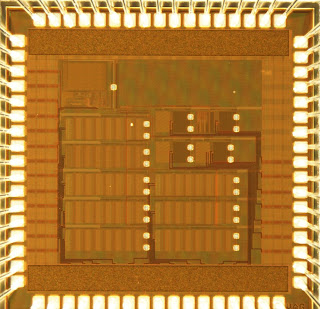

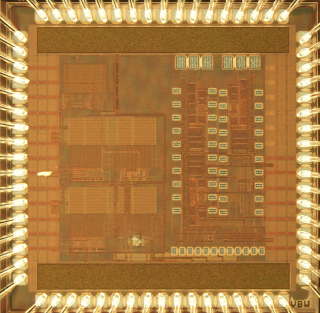

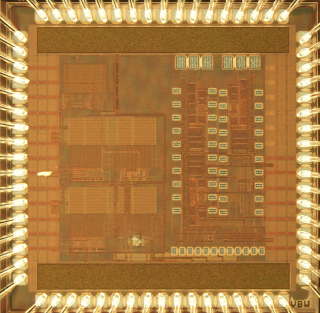

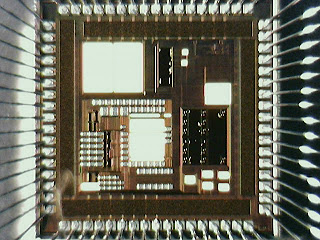

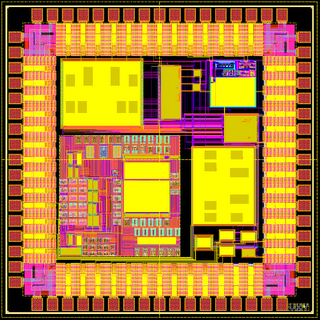

試作チップ20(65nm)

信頼性可変粗粒度再構成デバイス

プロセス: 65nm CMOS 12層配線プロセス

チップサイズ: 2mmx4mm

トランジスタ数: 7,143k

ゲート数: 1,787k

設計者: Dawood君,郡浦君,原田君、密山先生、橋本

テープアウト: 2010/2

チップ題目: 信頼性可変粗粒度再構成可能アレイ

概要:ソフトエラーによる集積回路の誤動作や経年劣化による摩耗故障が顕在化してきている. 我々は, アプリケーションと環境に

応じた信頼性への要求を実現する再構成可能デバイスの実現を目指して研究を進めている. 本試作では, これまでに開発を進めてき

た基本構成要素毎に冗長度を設定することで柔軟な信頼性を実現する信頼性可変粗粒度再構成可能アレイ[FPL, 2009]のプロトタ

イプ回路を実装した. 試作した再構成可能アレイ上にFIRフィルタなどの信号処理回路をマッピングし, アルファ線源を用いた加速

試験を行ったところ, 回路構成情報メモリ上のデータの平均寿命を測定することで, 異なるソフトエラー耐性を適応的な冗長構成に

よって実現できることを実証し, 信頼性(平均寿命)と使用リソース量のトレードオフを示した. さらに, 画像処理におけるソ

フトエラー耐性の評価環境を構築し, 2種類の異なる信頼性レベルにおけるソフトエラー耐性の違いを可視化することに成功した.

プロセス: 65nm CMOS 12層配線プロセス

チップサイズ: 2mmx4mm

トランジスタ数: 7,143k

ゲート数: 1,787k

設計者: Dawood君,郡浦君,原田君、密山先生、橋本

テープアウト: 2010/2

チップ題目: 信頼性可変粗粒度再構成可能アレイ

概要:ソフトエラーによる集積回路の誤動作や経年劣化による摩耗故障が顕在化してきている. 我々は, アプリケーションと環境に

応じた信頼性への要求を実現する再構成可能デバイスの実現を目指して研究を進めている. 本試作では, これまでに開発を進めてき

た基本構成要素毎に冗長度を設定することで柔軟な信頼性を実現する信頼性可変粗粒度再構成可能アレイ[FPL, 2009]のプロトタ

イプ回路を実装した. 試作した再構成可能アレイ上にFIRフィルタなどの信号処理回路をマッピングし, アルファ線源を用いた加速

試験を行ったところ, 回路構成情報メモリ上のデータの平均寿命を測定することで, 異なるソフトエラー耐性を適応的な冗長構成に

よって実現できることを実証し, 信頼性(平均寿命)と使用リソース量のトレードオフを示した. さらに, 画像処理におけるソ

フトエラー耐性の評価環境を構築し, 2種類の異なる信頼性レベルにおけるソフトエラー耐性の違いを可視化することに成功した.

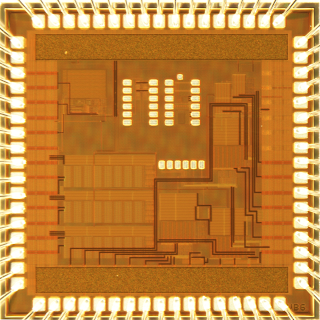

試作チップ19(65nm)

オンチップばらつきセンサ

プロセス: 65nm CMOS 12層配線プロセス

チップサイズ: 2mmx2mm

トランジスタ数: 約 691k トランジスタ (691,118)

ゲート数: 約 173k ゲート (172,780)

設計者: 新開君,橋本

テープアウト: 2009/12/10

プロセス: 65nm CMOS 12層配線プロセス

チップサイズ: 2mmx2mm

トランジスタ数: 約 691k トランジスタ (691,118)

ゲート数: 約 173k ゲート (172,780)

設計者: 新開君,橋本

テープアウト: 2009/12/10

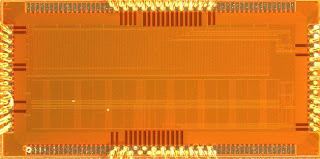

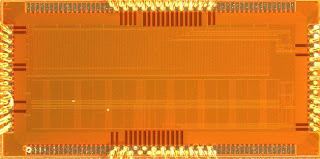

試作チップ18(65nm)

ソフトエラー耐性評価回路

プロセス: 65nm CMOS 12層配線プロセス

チップサイズ: 2mmx4mm

トランジスタ数: 3710k (SRAM以外)

ゲート数: 928k (SRAM以外)

設計者: 更田君,原田君,橋本

テープアウト: 2009/8

チップ題目: ソフトエラー耐性評価回路

概要: 本試作では、サブスレッショルドSRAMの中性子線に対するソフトエラー耐性を測定し、実用的なエラー耐性を有するかどうかを明らかにすることを目的とした。また、低電圧組み合わせ回路に発生する放射線起因一過性パルス(SET; single event transient)のパルス幅や一過性複数パルス(SEMT; single event multiple transients)確率を取得することも目的とした。本目的実現のため、0.3Vでも動作する256kb10T SRAM、electrical maskingを利用したSETパルス幅測定回路[ISQED, 2010]、ならびに新たなSEMT測定回路をチップ上に搭載した。大阪大学核物理センターにおいて実施した中性子照射実験では、SRAMを1.0Vから0.3Vの電源電圧で動作させ、ソフトエラー率の変化を測定した。また、複数ビット反転の電源電圧依存性や中性子ビーム照射角度への依存性も評価した.SETパルス幅測定については測定回路の動作は確認できたが、ターゲット回路の製造ばらつきによりSETのパルス幅の分布は得られなかった。また、SEMTの測定においては、SEMT発生割合の電源電圧依存性や基板バイアス依存性、空間的分布を測定した。

プロセス: 65nm CMOS 12層配線プロセス

チップサイズ: 2mmx4mm

トランジスタ数: 3710k (SRAM以外)

ゲート数: 928k (SRAM以外)

設計者: 更田君,原田君,橋本

テープアウト: 2009/8

チップ題目: ソフトエラー耐性評価回路

概要: 本試作では、サブスレッショルドSRAMの中性子線に対するソフトエラー耐性を測定し、実用的なエラー耐性を有するかどうかを明らかにすることを目的とした。また、低電圧組み合わせ回路に発生する放射線起因一過性パルス(SET; single event transient)のパルス幅や一過性複数パルス(SEMT; single event multiple transients)確率を取得することも目的とした。本目的実現のため、0.3Vでも動作する256kb10T SRAM、electrical maskingを利用したSETパルス幅測定回路[ISQED, 2010]、ならびに新たなSEMT測定回路をチップ上に搭載した。大阪大学核物理センターにおいて実施した中性子照射実験では、SRAMを1.0Vから0.3Vの電源電圧で動作させ、ソフトエラー率の変化を測定した。また、複数ビット反転の電源電圧依存性や中性子ビーム照射角度への依存性も評価した.SETパルス幅測定については測定回路の動作は確認できたが、ターゲット回路の製造ばらつきによりSETのパルス幅の分布は得られなかった。また、SEMTの測定においては、SEMT発生割合の電源電圧依存性や基板バイアス依存性、空間的分布を測定した。

試作チップ17(65nm)

信頼性可変粗粒度再構成デバイス

プロセス: 65nm CMOS 12層配線プロセス

チップサイズ: 2mmx2mm

トランジスタ数: ??

ゲート数: ??

設計者: Dawood君,郡浦君,密山先生、橋本

テープアウト: 2009/7

プロセス: 65nm CMOS 12層配線プロセス

チップサイズ: 2mmx2mm

トランジスタ数: ??

ゲート数: ??

設計者: Dawood君,郡浦君,密山先生、橋本

テープアウト: 2009/7

試作チップ16(65nm)

サブスレッショルドプロセッサ

プロセス: 65nm CMOS 12層配線プロセス

チップサイズ: 2mmx2mm

トランジスタ数: ??

ゲート数: ??

設計者: 更田君,黒田君,天木君、高井君、橋本

テープアウト: 2009/7

プロセス: 65nm CMOS 12層配線プロセス

チップサイズ: 2mmx2mm

トランジスタ数: ??

ゲート数: ??

設計者: 更田君,黒田君,天木君、高井君、橋本

テープアウト: 2009/7

試作チップ15(65nm)

タイミングエラー予告信号による適応的速度制御回路評価TEG

プロセス: 65nm CMOS 12層配線プロセス

チップサイズ: 2mmx2mm

トランジスタ数: ??

ゲート数: ??

設計者: 更田君,濱本君,橋本

テープアウト: 2008/11

題目: タイミングエラー予告信号による適応的速度制御回路評価TEG

概要:超低電力デジタル回路を実現する手法として, サブスレッショルド回路が注目

されている. サブスレッショルド回路とは,MOSトランジスタの閾値電圧よりも低い

電圧で動作する回路のことで, 低速・超低電力という特徴を有している. 一方で,

製造ばらつきや温度変化によって回路速度が大きく変動するという問題点があり,

従来のワーストケースを前にした回路設計では大きな設計マージンが必要となり

電力効率が悪い. したがって, 遅延変動を動的に検出し補償する回路が求められて

いる. 本チップでは, 加算器を対象として, タイミング余裕の検出回路を用いた

動的な速度制御回路の実装を行った. タイミング余裕の検出には, カナリアFFと

呼ばれるタイミングエラーを事前に予告する回路を適用し, 速度制御回路には,

基板バイアスにより制御を行う回路を実装した.本報告時点では加算器が正常に

動作することを確認しており, 今後詳細評価を進める予定である.

プロセス: 65nm CMOS 12層配線プロセス

チップサイズ: 2mmx2mm

トランジスタ数: ??

ゲート数: ??

設計者: 更田君,濱本君,橋本

テープアウト: 2008/11

題目: タイミングエラー予告信号による適応的速度制御回路評価TEG

概要:超低電力デジタル回路を実現する手法として, サブスレッショルド回路が注目

されている. サブスレッショルド回路とは,MOSトランジスタの閾値電圧よりも低い

電圧で動作する回路のことで, 低速・超低電力という特徴を有している. 一方で,

製造ばらつきや温度変化によって回路速度が大きく変動するという問題点があり,

従来のワーストケースを前にした回路設計では大きな設計マージンが必要となり

電力効率が悪い. したがって, 遅延変動を動的に検出し補償する回路が求められて

いる. 本チップでは, 加算器を対象として, タイミング余裕の検出回路を用いた

動的な速度制御回路の実装を行った. タイミング余裕の検出には, カナリアFFと

呼ばれるタイミングエラーを事前に予告する回路を適用し, 速度制御回路には,

基板バイアスにより制御を行う回路を実装した.本報告時点では加算器が正常に

動作することを確認しており, 今後詳細評価を進める予定である.

試作チップ14(65nm)

オンチップばらつきモニタ回路の試作

プロセス: 65nm CMOS 12層配線プロセス

チップサイズ: 2mmx2mm

トランジスタ数: 約 1M トランジスタ (1,011,714)

ゲート数: 約 250k ゲート (252,929)

設計者: 阿部君,原田君,天木君,橋本

テープアウト: 2008/11/20

VDEC年報2009の記事です。

題目: オンチップばらつきモニタ回路の試作

概要:本試作では, 製造ばらつき, 環境変動のセンシング技術確立のため, 簡潔かつ

性能補償に必要な情報が得られるセンサの開発を目標とし, 以下のテストチップを

設計した. 試作回路の基本ブロックであるばらつきセンサブロックは, デコーダや

セレクタ, 複数種類のROで構成される. 規則的にばらつきセンサブロックを敷き詰める

ことで, 近隣ブロックのROの特性との平均を取り,より多くの段数時のばらつき情報が

近似的に得られる. また, NMOS/PMOSのWを変則的に変えたROの発振結果を用いて, 応答

曲面法によりNMOS/PMOSのばらつき推定・分離を行う. そして, 推定したNMOS/PMOS

ばらつき情報をもとに, 制御用ROに基板バイアスをかけ, 発振周波数やリーク電流などの

変化を観測する. この観測結果とトランジスタ単体の特性を比較することで, 推定

したNMOS/PMOS ばらつきの妥当性を評価する. 現在までに, 発振信号が出力され,

セレクト信号を変化させると発振信号も変化することを確認している.

プロセス: 65nm CMOS 12層配線プロセス

チップサイズ: 2mmx2mm

トランジスタ数: 約 1M トランジスタ (1,011,714)

ゲート数: 約 250k ゲート (252,929)

設計者: 阿部君,原田君,天木君,橋本

テープアウト: 2008/11/20

VDEC年報2009の記事です。

題目: オンチップばらつきモニタ回路の試作

概要:本試作では, 製造ばらつき, 環境変動のセンシング技術確立のため, 簡潔かつ

性能補償に必要な情報が得られるセンサの開発を目標とし, 以下のテストチップを

設計した. 試作回路の基本ブロックであるばらつきセンサブロックは, デコーダや

セレクタ, 複数種類のROで構成される. 規則的にばらつきセンサブロックを敷き詰める

ことで, 近隣ブロックのROの特性との平均を取り,より多くの段数時のばらつき情報が

近似的に得られる. また, NMOS/PMOSのWを変則的に変えたROの発振結果を用いて, 応答

曲面法によりNMOS/PMOSのばらつき推定・分離を行う. そして, 推定したNMOS/PMOS

ばらつき情報をもとに, 制御用ROに基板バイアスをかけ, 発振周波数やリーク電流などの

変化を観測する. この観測結果とトランジスタ単体の特性を比較することで, 推定

したNMOS/PMOS ばらつきの妥当性を評価する. 現在までに, 発振信号が出力され,

セレクト信号を変化させると発振信号も変化することを確認している.

試作チップ13(180nm)

周期ゆらぎを利用した真性乱数生成回路

プロセス: 180nm CMOS5層アルミ配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 1,000~10,000トランジスタ

ゲート数: ?ゲート

設計者: 天木君、橋本

テープアウト: 2008/7

VDEC年報2009の記事です。

チップ題目: オシレータサンプリング方式乱数生成回路

概要:熱雑音などのランダムな物理現象から生成される物理乱数がある.中でも各ビット同

士が無相関であり, 1/0の出現確率が等しいものを真性乱数といい, セキュリティ用途に適

する. 本回路では, 低速高速の二つのオシレータを使用する, オシレータサンプリング方式

の真性乱数生成回路を実装した. 本回路では低速オシレータに分周器を繋いでおり, 分周に

よる乱数品質への影響を調べることができる. また, 高速オシレータを構成するインバータ

一つおきに, Nウェル電位を外部から与えることが可能となっている. これにより高速オシ

レータのデューティ比を調節し, デューティ比が乱数品質に与える影響についても調べるこ

とができる. 実測により, 基板電位を外部から与えない乱数生成回路については, ランダム

らしきビット列を得られることを確認した. IOまわりに不具合があり, 基板電位を与える

ピンとVDDOの間の抵抗を測定したところ, 300オーム程度しかなかった. そのためか, 基

板電位を外部から与えるように設計した乱数生成回路については動作を確認できなかった.

プロセス: 180nm CMOS5層アルミ配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 1,000~10,000トランジスタ

ゲート数: ?ゲート

設計者: 天木君、橋本

テープアウト: 2008/7

VDEC年報2009の記事です。

チップ題目: オシレータサンプリング方式乱数生成回路

概要:熱雑音などのランダムな物理現象から生成される物理乱数がある.中でも各ビット同

士が無相関であり, 1/0の出現確率が等しいものを真性乱数といい, セキュリティ用途に適

する. 本回路では, 低速高速の二つのオシレータを使用する, オシレータサンプリング方式

の真性乱数生成回路を実装した. 本回路では低速オシレータに分周器を繋いでおり, 分周に

よる乱数品質への影響を調べることができる. また, 高速オシレータを構成するインバータ

一つおきに, Nウェル電位を外部から与えることが可能となっている. これにより高速オシ

レータのデューティ比を調節し, デューティ比が乱数品質に与える影響についても調べるこ

とができる. 実測により, 基板電位を外部から与えない乱数生成回路については, ランダム

らしきビット列を得られることを確認した. IOまわりに不具合があり, 基板電位を与える

ピンとVDDOの間の抵抗を測定したところ, 300オーム程度しかなかった. そのためか, 基

板電位を外部から与えるように設計した乱数生成回路については動作を確認できなかった.

Tuesday, March 25, 2008

試作チップ11(90nm)

ダイナミック電源ノイズ波形測定の第2弾。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 200,000トランジスタ

ゲート数: 50,000ゲート

設計者: 小笠原君、橋本

テープアウト: 2007/7

VDEC年報2007の記事です。

チップ題目: オンチップ電源ノイズ評価TEG (AS9007_2)

チップ概要:

本試作では電源ノイズによる電源電圧変動を測定する回路を実装し、電源ノイズの測定を試みた。

ノイズ測定回路はリングオシレータを基にした回路で、インバータとトランスミッションゲートから

構成される[1]。この回路はデジタル回路素子のみで電源ノイズ波形を観測することが可能である。

前回試作より改良を行い、サンプリング性能の向上を試みた。測定結果から、電源ノイズ測定回路の

動作、および性能を確認した。施した改良により、サンプリング性能(速度、電圧分解能)の向上など

が確認された。この回路を用いて電源ノイズ波形を測定し、デカップリング容量、基板等による電源

ノイズ低減の効果の検証を行った。

[1] Y. Ogasahara, M. Hashimoto, and T. Onoye, ``Dynamic Supply Noise Measurement with All

Digital Gated Oscillator for Evaluating Decoupling Capacitance Effect,'' Proc. CICC, pp.783-786, 2007

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 200,000トランジスタ

ゲート数: 50,000ゲート

設計者: 小笠原君、橋本

テープアウト: 2007/7

VDEC年報2007の記事です。

チップ題目: オンチップ電源ノイズ評価TEG (AS9007_2)

チップ概要:

本試作では電源ノイズによる電源電圧変動を測定する回路を実装し、電源ノイズの測定を試みた。

ノイズ測定回路はリングオシレータを基にした回路で、インバータとトランスミッションゲートから

構成される[1]。この回路はデジタル回路素子のみで電源ノイズ波形を観測することが可能である。

前回試作より改良を行い、サンプリング性能の向上を試みた。測定結果から、電源ノイズ測定回路の

動作、および性能を確認した。施した改良により、サンプリング性能(速度、電圧分解能)の向上など

が確認された。この回路を用いて電源ノイズ波形を測定し、デカップリング容量、基板等による電源

ノイズ低減の効果の検証を行った。

[1] Y. Ogasahara, M. Hashimoto, and T. Onoye, ``Dynamic Supply Noise Measurement with All

Digital Gated Oscillator for Evaluating Decoupling Capacitance Effect,'' Proc. CICC, pp.783-786, 2007

試作チップ12(90nm)

ダイナミック電源ノイズ波形測定の第3弾。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: ???トランジスタ

ゲート数: ???ゲート

設計者: 小笠原君、更田君、濱本君、橋本

テープアウト: 2007/10

VDEC年報2007の記事です。

チップ題目: デカップリング容量評価TEGおよびタイミング余裕検出回路評価TEG (AS9007_3)

チップ概要:

本チップは2つの回路からなる。1) 近年のプロセスにおけるSoCの物理設計では電源ノイズの考慮と対策が必要不可欠となっている。デカップリング容量は電源ノイズ対策で頻繁に用いられるが、トランジスタのゲート容量を利用するため、面積オーバーヘッドやゲートリーク電流の問題が存在する。本チップでは、面積あたりの電源ノイズ低減効果を大きくすることのできる手法を用いたデカップリング容量を実装した。本試作チップを用いて測定を行い、実装した回路素子の動作、特性を検証すると同時に、測定結果に基づいてより効率的な設計について検討を行う予定である。2) サブスレッショルド回路は、製造ばらつきや温度変化によって回路動作速度が大きく変動する問題点がある。ワーストケースを前提にした回路設計では大きな設計マージンが必要であり電力効率が悪い。製造後に遅延変動を動的に検出し補償する回路が求められている。本チップでは、動的にタイミング余裕を検出する回路を実装した。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: ???トランジスタ

ゲート数: ???ゲート

設計者: 小笠原君、更田君、濱本君、橋本

テープアウト: 2007/10

VDEC年報2007の記事です。

チップ題目: デカップリング容量評価TEGおよびタイミング余裕検出回路評価TEG (AS9007_3)

チップ概要:

本チップは2つの回路からなる。1) 近年のプロセスにおけるSoCの物理設計では電源ノイズの考慮と対策が必要不可欠となっている。デカップリング容量は電源ノイズ対策で頻繁に用いられるが、トランジスタのゲート容量を利用するため、面積オーバーヘッドやゲートリーク電流の問題が存在する。本チップでは、面積あたりの電源ノイズ低減効果を大きくすることのできる手法を用いたデカップリング容量を実装した。本試作チップを用いて測定を行い、実装した回路素子の動作、特性を検証すると同時に、測定結果に基づいてより効率的な設計について検討を行う予定である。2) サブスレッショルド回路は、製造ばらつきや温度変化によって回路動作速度が大きく変動する問題点がある。ワーストケースを前提にした回路設計では大きな設計マージンが必要であり電力効率が悪い。製造後に遅延変動を動的に検出し補償する回路が求められている。本チップでは、動的にタイミング余裕を検出する回路を実装した。

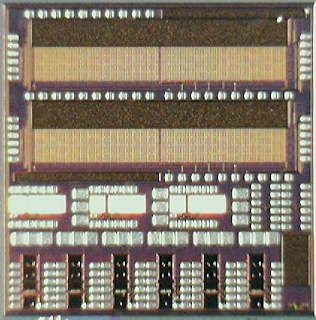

試作チップ10(90nm)

ばらつき測定用デバイスアレイ。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: ???トランジスタ

ゲート数: ???ゲート

設計者: 更田君、濱本君、橋本

テープアウト: 2007/7

VDEC年報2007の記事です。

チップ題目: サブスレッショルド特性ばらつき評価アレイ回路 (AS9007_1)

チップ概要:

超低電力CMOSデジタル回路を実現する手法として、サブスレッショルド回路が注目されている。サブスレッショルド回路とは、トランジスタの閾値電圧よりも低い電圧で動作する回路のことで、低速・低消費電力という特徴を有している。一方で、製造ばらつきによりその特性が大きく変動するという問題点がある。本チップでは、サブスレッショルド回路における製造ばらつきの影響を測定・評価するために、NMOS/PMOSとリングオシレータをアレイ状に配置した回路を設計した。本回路では、6400個のトランジスタの電流電圧特性と、2800個のリングオシレータの発振周波数を測定できる。また、各デバイスに対して、任意の基板バイアス電圧を印加して測定できるよう設計を行った。本アレイ回路の測定を行い、サブスレッショルド特性のばらつきのモデル化・検証を行った。基板バイアスによる特性の制御性についても評価を行った。また、本回路とは別に、基板バイアス電圧を印加する位置と制御性の関係を観測する回路を実装した。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: ???トランジスタ

ゲート数: ???ゲート

設計者: 更田君、濱本君、橋本

テープアウト: 2007/7

VDEC年報2007の記事です。

チップ題目: サブスレッショルド特性ばらつき評価アレイ回路 (AS9007_1)

チップ概要:

超低電力CMOSデジタル回路を実現する手法として、サブスレッショルド回路が注目されている。サブスレッショルド回路とは、トランジスタの閾値電圧よりも低い電圧で動作する回路のことで、低速・低消費電力という特徴を有している。一方で、製造ばらつきによりその特性が大きく変動するという問題点がある。本チップでは、サブスレッショルド回路における製造ばらつきの影響を測定・評価するために、NMOS/PMOSとリングオシレータをアレイ状に配置した回路を設計した。本回路では、6400個のトランジスタの電流電圧特性と、2800個のリングオシレータの発振周波数を測定できる。また、各デバイスに対して、任意の基板バイアス電圧を印加して測定できるよう設計を行った。本アレイ回路の測定を行い、サブスレッショルド特性のばらつきのモデル化・検証を行った。基板バイアスによる特性の制御性についても評価を行った。また、本回路とは別に、基板バイアス電圧を印加する位置と制御性の関係を観測する回路を実装した。

Monday, January 29, 2007

試作チップ9(0.35um)

無歪み伝送線路の特性を評価するためのテストチップの第2弾。UCSDのCK Cheng先生、京都大学土谷亮先生との共同研究です。電源ノイズ低減技術に関するテスト回路も搭載しています。

プロセス: 0.35um CMOS 3層アルミ配線プロセス

チップサイズ: 4.9mmX4.9mm

テープアウト: 2007年1月22日

設計者: 橋本

VDEC年報2007の記事です。

チップ題目: オンチップ伝送線路と電源ノイズ評価TEG

チップ概要:

本試作では波形歪みの小さいオンチップ伝送線路を搭載した。無歪み条件を部分的に満たすように、意図的に配線にシャントコンダクタンスを挿入し、伝送特性の周波数依存性を低下させる。本伝送線路の波形歪み低減効果を時間領域で評価するため、パターンジェネレータとオシロスコープを用いて、オンウェハプロービングでアイダイアグラムを測定する。別に、オンチップ電源ノイズ低減のため、デカップリング容量、ならびにスタブ伝送線路を付加した電源ノイズ発生回路を搭載した。消費電流の周波数成分の測定やアクティブプローブを用いた電源ノイズ波形を観測し、低減されるノイズの周波数成分を評価する。現在、いずれのテスト回路についても評価の準備を進めている。

[1] M. Hashimoto, J. Siriporn, A. Tsuchiya, H. Zhu, and C.-K. Cheng,

``Analytical Eye-Diagram Model for On-Chip Distortionless Transmission

Lines and Its Application to Design Space Exploration,'' Proc. CICC,

pp.869--872, 2007.

プロセス: 0.35um CMOS 3層アルミ配線プロセス

チップサイズ: 4.9mmX4.9mm

テープアウト: 2007年1月22日

設計者: 橋本

VDEC年報2007の記事です。

チップ題目: オンチップ伝送線路と電源ノイズ評価TEG

チップ概要:

本試作では波形歪みの小さいオンチップ伝送線路を搭載した。無歪み条件を部分的に満たすように、意図的に配線にシャントコンダクタンスを挿入し、伝送特性の周波数依存性を低下させる。本伝送線路の波形歪み低減効果を時間領域で評価するため、パターンジェネレータとオシロスコープを用いて、オンウェハプロービングでアイダイアグラムを測定する。別に、オンチップ電源ノイズ低減のため、デカップリング容量、ならびにスタブ伝送線路を付加した電源ノイズ発生回路を搭載した。消費電流の周波数成分の測定やアクティブプローブを用いた電源ノイズ波形を観測し、低減されるノイズの周波数成分を評価する。現在、いずれのテスト回路についても評価の準備を進めている。

[1] M. Hashimoto, J. Siriporn, A. Tsuchiya, H. Zhu, and C.-K. Cheng,

``Analytical Eye-Diagram Model for On-Chip Distortionless Transmission

Lines and Its Application to Design Space Exploration,'' Proc. CICC,

pp.869--872, 2007.

Friday, December 08, 2006

試作チップ8(90nm)

基板バイアスによる速度可変機構を持ったリンコンフィギャラブルデバイスの試作。 密山先生とともに研究を進めています。

基板コンタクト、トランジスタ間距離と基板電位制御性の関係を評価するためのリングオシレータTEGについて、測定結果をGLSVLSI2008, SASIMI2007で発表しました。SASIMI2007ではOutstanding paper awardを受賞しました。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 240,000トランジスタ

ゲート数: 60,000ゲート

メモリ量: 1.7kbyteメモリ

設計者: 高橋君、濱本君、更田君、密山先生、橋本

VDEC年報2006の記事です。

チップ題目: 加算器のサブスレッショルド動作評価回路、および基板電位制御の評価回路 (AS9006_4)

チップ概要:

本チップは3つの回路からなる.(1) 電源電圧をサブスレッショルド領域まで低

くすると,低速だが非常に低消費電力な回路が実現できる.本チップでは,サブ

スレッショルド領域での加算器の動作を評価する回路の設計を行った.32ビット

加算器を7種類搭載し,それぞれで動作速度と消費電力を測定する.(2)基板電位

を変化させることで,MOSの特性を制御できることが知られている.本チップで

は,MOSから基板電位を印加する位置までの距離を変えて,制御性の差異を観測

する回路を設計した.測定対象としてリングオシレータを用い,基板電位印加位

置までの距離と発振周期を測定することで,制御性の評価を行う.(3) 低電圧回

路ではラッチアップの危険性が低下するため,従来とは違ったレイアウトによる

基板電位の印加方法が考えられる.本チップでは,3種類のレイアウトにより基

板電位制御回路を設計した.各レイアウトの制御性をALU・乗算器などにより確

認する.現在,チップの実測・評価を行っている.

基板コンタクト、トランジスタ間距離と基板電位制御性の関係を評価するためのリングオシレータTEGについて、測定結果をGLSVLSI2008, SASIMI2007で発表しました。SASIMI2007ではOutstanding paper awardを受賞しました。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 240,000トランジスタ

ゲート数: 60,000ゲート

メモリ量: 1.7kbyteメモリ

設計者: 高橋君、濱本君、更田君、密山先生、橋本

VDEC年報2006の記事です。

チップ題目: 加算器のサブスレッショルド動作評価回路、および基板電位制御の評価回路 (AS9006_4)

チップ概要:

本チップは3つの回路からなる.(1) 電源電圧をサブスレッショルド領域まで低

くすると,低速だが非常に低消費電力な回路が実現できる.本チップでは,サブ

スレッショルド領域での加算器の動作を評価する回路の設計を行った.32ビット

加算器を7種類搭載し,それぞれで動作速度と消費電力を測定する.(2)基板電位

を変化させることで,MOSの特性を制御できることが知られている.本チップで

は,MOSから基板電位を印加する位置までの距離を変えて,制御性の差異を観測

する回路を設計した.測定対象としてリングオシレータを用い,基板電位印加位

置までの距離と発振周期を測定することで,制御性の評価を行う.(3) 低電圧回

路ではラッチアップの危険性が低下するため,従来とは違ったレイアウトによる

基板電位の印加方法が考えられる.本チップでは,3種類のレイアウトにより基

板電位制御回路を設計した.各レイアウトの制御性をALU・乗算器などにより確

認する.現在,チップの実測・評価を行っている.

試作チップ7(90nm)

ダイナミック電源ノイズ波形測定。本研究成果について、CICC2007, ASP-DAC2008で発表を行いました。ASP-DAC2008 では University LSI Design Contestで、Special Feature Awardを受賞しました。2008年第10回LSI IPデザインアワードで研究助成賞を受賞しました。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 400,000

ゲート数: 100,000

テープアウト日:2006/11/19

設計者: 小笠原君、橋本

VDEC年報2006の記事です。

チップ題目: 電源ノイズ波形測定TEG(AS9006_6)

チップ概要:

本試作では電源ノイズによる電源電圧変動を測定する回路を実装し、

電源ノイズを測定することを目的とする。電源ノイズ測定回路は1つのTEGにつき、

動作段数が可変であるNANDゲート12段を512個配置して電源ノイズを発生させる。

各種の条件を変えて配置したTEGの数は12個である。

電源ノイズ波形測定回路は繰り返し発生する

ノイズ波形をサンプリングし、電源ノイズの波形を測定する回路である。

ノイズ発生回路、電源ノイズ測定回路はPLLの生成する

クロックに同期して動作する。

ノイズ測定回路を用いてオンチップに意図的に追加される、

または必然的に寄生する容量が電源ノイズに与える影響を測定する。

測定結果から、実装した電源ノイズ測定回路が電源ノイズ波形を

サンプリングすることが可能であることを確認し、

今後このプロセスにおける測定回路のサンプリング性能限界、

電圧精度などの情報を得る予定である。

各TEGの測定結果の比較から、オンチップに付加される、

または寄生する容量が電源ノイズに与える影響を観測した。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 400,000

ゲート数: 100,000

テープアウト日:2006/11/19

設計者: 小笠原君、橋本

VDEC年報2006の記事です。

チップ題目: 電源ノイズ波形測定TEG(AS9006_6)

チップ概要:

本試作では電源ノイズによる電源電圧変動を測定する回路を実装し、

電源ノイズを測定することを目的とする。電源ノイズ測定回路は1つのTEGにつき、

動作段数が可変であるNANDゲート12段を512個配置して電源ノイズを発生させる。

各種の条件を変えて配置したTEGの数は12個である。

電源ノイズ波形測定回路は繰り返し発生する

ノイズ波形をサンプリングし、電源ノイズの波形を測定する回路である。

ノイズ発生回路、電源ノイズ測定回路はPLLの生成する

クロックに同期して動作する。

ノイズ測定回路を用いてオンチップに意図的に追加される、

または必然的に寄生する容量が電源ノイズに与える影響を測定する。

測定結果から、実装した電源ノイズ測定回路が電源ノイズ波形を

サンプリングすることが可能であることを確認し、

今後このプロセスにおける測定回路のサンプリング性能限界、

電圧精度などの情報を得る予定である。

各TEGの測定結果の比較から、オンチップに付加される、

または寄生する容量が電源ノイズに与える影響を観測した。