Friday, December 08, 2006

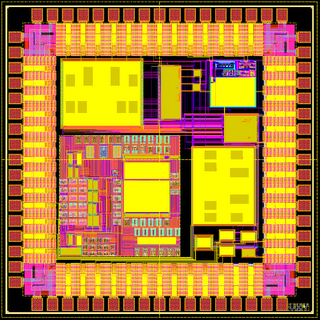

試作チップ8(90nm)

基板バイアスによる速度可変機構を持ったリンコンフィギャラブルデバイスの試作。 密山先生とともに研究を進めています。

基板コンタクト、トランジスタ間距離と基板電位制御性の関係を評価するためのリングオシレータTEGについて、測定結果をGLSVLSI2008, SASIMI2007で発表しました。SASIMI2007ではOutstanding paper awardを受賞しました。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 240,000トランジスタ

ゲート数: 60,000ゲート

メモリ量: 1.7kbyteメモリ

設計者: 高橋君、濱本君、更田君、密山先生、橋本

VDEC年報2006の記事です。

チップ題目: 加算器のサブスレッショルド動作評価回路、および基板電位制御の評価回路 (AS9006_4)

チップ概要:

本チップは3つの回路からなる.(1) 電源電圧をサブスレッショルド領域まで低

くすると,低速だが非常に低消費電力な回路が実現できる.本チップでは,サブ

スレッショルド領域での加算器の動作を評価する回路の設計を行った.32ビット

加算器を7種類搭載し,それぞれで動作速度と消費電力を測定する.(2)基板電位

を変化させることで,MOSの特性を制御できることが知られている.本チップで

は,MOSから基板電位を印加する位置までの距離を変えて,制御性の差異を観測

する回路を設計した.測定対象としてリングオシレータを用い,基板電位印加位

置までの距離と発振周期を測定することで,制御性の評価を行う.(3) 低電圧回

路ではラッチアップの危険性が低下するため,従来とは違ったレイアウトによる

基板電位の印加方法が考えられる.本チップでは,3種類のレイアウトにより基

板電位制御回路を設計した.各レイアウトの制御性をALU・乗算器などにより確

認する.現在,チップの実測・評価を行っている.

基板コンタクト、トランジスタ間距離と基板電位制御性の関係を評価するためのリングオシレータTEGについて、測定結果をGLSVLSI2008, SASIMI2007で発表しました。SASIMI2007ではOutstanding paper awardを受賞しました。

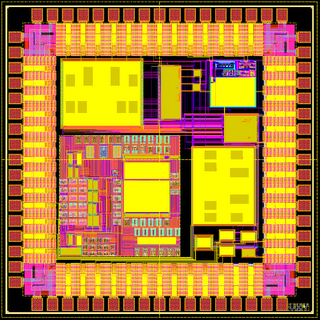

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 240,000トランジスタ

ゲート数: 60,000ゲート

メモリ量: 1.7kbyteメモリ

設計者: 高橋君、濱本君、更田君、密山先生、橋本

VDEC年報2006の記事です。

チップ題目: 加算器のサブスレッショルド動作評価回路、および基板電位制御の評価回路 (AS9006_4)

チップ概要:

本チップは3つの回路からなる.(1) 電源電圧をサブスレッショルド領域まで低

くすると,低速だが非常に低消費電力な回路が実現できる.本チップでは,サブ

スレッショルド領域での加算器の動作を評価する回路の設計を行った.32ビット

加算器を7種類搭載し,それぞれで動作速度と消費電力を測定する.(2)基板電位

を変化させることで,MOSの特性を制御できることが知られている.本チップで

は,MOSから基板電位を印加する位置までの距離を変えて,制御性の差異を観測

する回路を設計した.測定対象としてリングオシレータを用い,基板電位印加位

置までの距離と発振周期を測定することで,制御性の評価を行う.(3) 低電圧回

路ではラッチアップの危険性が低下するため,従来とは違ったレイアウトによる

基板電位の印加方法が考えられる.本チップでは,3種類のレイアウトにより基

板電位制御回路を設計した.各レイアウトの制御性をALU・乗算器などにより確

認する.現在,チップの実測・評価を行っている.