Friday, December 08, 2006

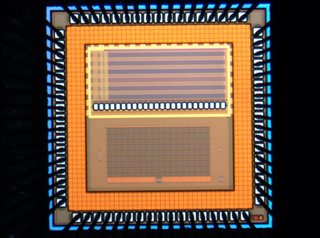

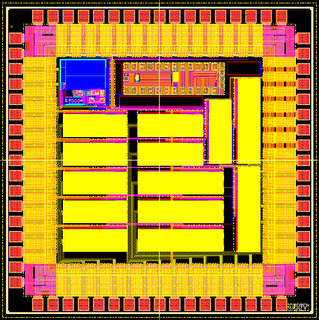

試作チップ8(90nm)

基板バイアスによる速度可変機構を持ったリンコンフィギャラブルデバイスの試作。 密山先生とともに研究を進めています。

基板コンタクト、トランジスタ間距離と基板電位制御性の関係を評価するためのリングオシレータTEGについて、測定結果をGLSVLSI2008, SASIMI2007で発表しました。SASIMI2007ではOutstanding paper awardを受賞しました。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 240,000トランジスタ

ゲート数: 60,000ゲート

メモリ量: 1.7kbyteメモリ

設計者: 高橋君、濱本君、更田君、密山先生、橋本

VDEC年報2006の記事です。

チップ題目: 加算器のサブスレッショルド動作評価回路、および基板電位制御の評価回路 (AS9006_4)

チップ概要:

本チップは3つの回路からなる.(1) 電源電圧をサブスレッショルド領域まで低

くすると,低速だが非常に低消費電力な回路が実現できる.本チップでは,サブ

スレッショルド領域での加算器の動作を評価する回路の設計を行った.32ビット

加算器を7種類搭載し,それぞれで動作速度と消費電力を測定する.(2)基板電位

を変化させることで,MOSの特性を制御できることが知られている.本チップで

は,MOSから基板電位を印加する位置までの距離を変えて,制御性の差異を観測

する回路を設計した.測定対象としてリングオシレータを用い,基板電位印加位

置までの距離と発振周期を測定することで,制御性の評価を行う.(3) 低電圧回

路ではラッチアップの危険性が低下するため,従来とは違ったレイアウトによる

基板電位の印加方法が考えられる.本チップでは,3種類のレイアウトにより基

板電位制御回路を設計した.各レイアウトの制御性をALU・乗算器などにより確

認する.現在,チップの実測・評価を行っている.

基板コンタクト、トランジスタ間距離と基板電位制御性の関係を評価するためのリングオシレータTEGについて、測定結果をGLSVLSI2008, SASIMI2007で発表しました。SASIMI2007ではOutstanding paper awardを受賞しました。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 240,000トランジスタ

ゲート数: 60,000ゲート

メモリ量: 1.7kbyteメモリ

設計者: 高橋君、濱本君、更田君、密山先生、橋本

VDEC年報2006の記事です。

チップ題目: 加算器のサブスレッショルド動作評価回路、および基板電位制御の評価回路 (AS9006_4)

チップ概要:

本チップは3つの回路からなる.(1) 電源電圧をサブスレッショルド領域まで低

くすると,低速だが非常に低消費電力な回路が実現できる.本チップでは,サブ

スレッショルド領域での加算器の動作を評価する回路の設計を行った.32ビット

加算器を7種類搭載し,それぞれで動作速度と消費電力を測定する.(2)基板電位

を変化させることで,MOSの特性を制御できることが知られている.本チップで

は,MOSから基板電位を印加する位置までの距離を変えて,制御性の差異を観測

する回路を設計した.測定対象としてリングオシレータを用い,基板電位印加位

置までの距離と発振周期を測定することで,制御性の評価を行う.(3) 低電圧回

路ではラッチアップの危険性が低下するため,従来とは違ったレイアウトによる

基板電位の印加方法が考えられる.本チップでは,3種類のレイアウトにより基

板電位制御回路を設計した.各レイアウトの制御性をALU・乗算器などにより確

認する.現在,チップの実測・評価を行っている.

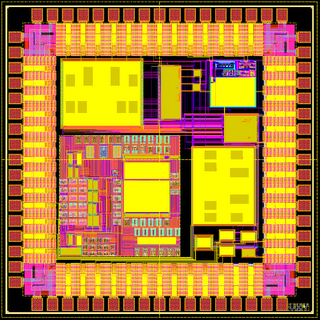

試作チップ7(90nm)

ダイナミック電源ノイズ波形測定。本研究成果について、CICC2007, ASP-DAC2008で発表を行いました。ASP-DAC2008 では University LSI Design Contestで、Special Feature Awardを受賞しました。2008年第10回LSI IPデザインアワードで研究助成賞を受賞しました。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 400,000

ゲート数: 100,000

テープアウト日:2006/11/19

設計者: 小笠原君、橋本

VDEC年報2006の記事です。

チップ題目: 電源ノイズ波形測定TEG(AS9006_6)

チップ概要:

本試作では電源ノイズによる電源電圧変動を測定する回路を実装し、

電源ノイズを測定することを目的とする。電源ノイズ測定回路は1つのTEGにつき、

動作段数が可変であるNANDゲート12段を512個配置して電源ノイズを発生させる。

各種の条件を変えて配置したTEGの数は12個である。

電源ノイズ波形測定回路は繰り返し発生する

ノイズ波形をサンプリングし、電源ノイズの波形を測定する回路である。

ノイズ発生回路、電源ノイズ測定回路はPLLの生成する

クロックに同期して動作する。

ノイズ測定回路を用いてオンチップに意図的に追加される、

または必然的に寄生する容量が電源ノイズに与える影響を測定する。

測定結果から、実装した電源ノイズ測定回路が電源ノイズ波形を

サンプリングすることが可能であることを確認し、

今後このプロセスにおける測定回路のサンプリング性能限界、

電圧精度などの情報を得る予定である。

各TEGの測定結果の比較から、オンチップに付加される、

または寄生する容量が電源ノイズに与える影響を観測した。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 400,000

ゲート数: 100,000

テープアウト日:2006/11/19

設計者: 小笠原君、橋本

VDEC年報2006の記事です。

チップ題目: 電源ノイズ波形測定TEG(AS9006_6)

チップ概要:

本試作では電源ノイズによる電源電圧変動を測定する回路を実装し、

電源ノイズを測定することを目的とする。電源ノイズ測定回路は1つのTEGにつき、

動作段数が可変であるNANDゲート12段を512個配置して電源ノイズを発生させる。

各種の条件を変えて配置したTEGの数は12個である。

電源ノイズ波形測定回路は繰り返し発生する

ノイズ波形をサンプリングし、電源ノイズの波形を測定する回路である。

ノイズ発生回路、電源ノイズ測定回路はPLLの生成する

クロックに同期して動作する。

ノイズ測定回路を用いてオンチップに意図的に追加される、

または必然的に寄生する容量が電源ノイズに与える影響を測定する。

測定結果から、実装した電源ノイズ測定回路が電源ノイズ波形を

サンプリングすることが可能であることを確認し、

今後このプロセスにおける測定回路のサンプリング性能限界、

電圧精度などの情報を得る予定である。

各TEGの測定結果の比較から、オンチップに付加される、

または寄生する容量が電源ノイズに与える影響を観測した。

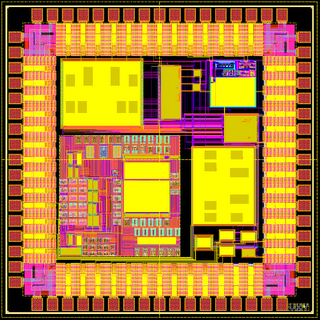

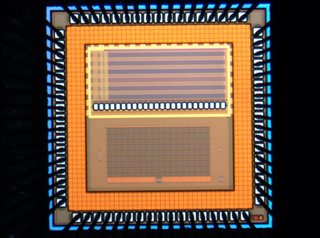

試作チップ6(90nm)

リンコンフィギャラブルデバイスの試作。 密山先生とともに研究を進めています。現在、M2の高橋君が測定中。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 700,000トランジスタ

ゲート数: 175,000ゲート

メモリ量: 6.7kbyteメモリ

設計者: 高橋君、密山先生、更田君、橋本

VDEC年報2006の記事です。

チップ題目: メディア処理向け小面積リコンフィギュラブルプロセッサ (AS9006_5)

チップ概要:

従来のリコンフィギュラブルプロセッサは,高い性能と柔軟性を併せ持つ反面,

専用回路と比較して遥かに大きい回路面積が課題となっている.そこで,対象

アプリケーションを動画像復号化処理に絞りアーキテクチャの効率化を図るこ

とで,従来アーキテクチャと比較して大幅な小面積化を実現するリコンフィギュ

ラブルプロセッサを提案してきた.本試作では,検証用回路も含んたプロトタ

イプチップを試作した.一部回路の不具合により,リコンフィギュラブルプロ

セッサ全体としての動作は確認できなかったが,提案アーキテクチャの実装可

能性・有効性を確認することができた.また,基板バイアスによる特性変化を

評価するTEGも搭載し,測定により基本特性に関する知見を得た.

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 700,000トランジスタ

ゲート数: 175,000ゲート

メモリ量: 6.7kbyteメモリ

設計者: 高橋君、密山先生、更田君、橋本

VDEC年報2006の記事です。

チップ題目: メディア処理向け小面積リコンフィギュラブルプロセッサ (AS9006_5)

チップ概要:

従来のリコンフィギュラブルプロセッサは,高い性能と柔軟性を併せ持つ反面,

専用回路と比較して遥かに大きい回路面積が課題となっている.そこで,対象

アプリケーションを動画像復号化処理に絞りアーキテクチャの効率化を図るこ

とで,従来アーキテクチャと比較して大幅な小面積化を実現するリコンフィギュ

ラブルプロセッサを提案してきた.本試作では,検証用回路も含んたプロトタ

イプチップを試作した.一部回路の不具合により,リコンフィギュラブルプロ

セッサ全体としての動作は確認できなかったが,提案アーキテクチャの実装可

能性・有効性を確認することができた.また,基板バイアスによる特性変化を

評価するTEGも搭載し,測定により基本特性に関する知見を得た.

試作チップ5(90nm)

ダイナミック電源ノイズ波形測定。不具合があり目的を達せられず。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 400,000

ゲート数: 100,000

テープアウト日: 2006/7/14

設計者: 小笠原君、更田君、橋本

以下はVDEC年報2006の記事です。

チップ題目:電源ノイズ波形測定とMOS基板電位特性測定TEG (AS9006_2)

チップ概要:

本試作では電源ノイズによる電源電圧変動を測定する回路を実装し、

電源ノイズの測定を試みた。ノイズ測定回路は繰り返し発生するノイズ波形を

サンプリングし、電源ノイズの波形を測定する回路である。

ノイズ測定回路を用いてデカップリング容量が電源ノイズに与える影響、

およびデカップリング容量の特性の測定を試みる。

また、基板電位を分離したMOSFETの基本特性測定回路を実装し、

基板電位を変化させた際のMOSFET特性を測定する。

測定結果から、電源ノイズ測定回路の動作を一部確認した。

また、基板電位を変化させることによりMOSFETの特性が変化することを

測定で確認し、基板電位とデバイス特性の基礎的なデータを得た。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 400,000

ゲート数: 100,000

テープアウト日: 2006/7/14

設計者: 小笠原君、更田君、橋本

以下はVDEC年報2006の記事です。

チップ題目:電源ノイズ波形測定とMOS基板電位特性測定TEG (AS9006_2)

チップ概要:

本試作では電源ノイズによる電源電圧変動を測定する回路を実装し、

電源ノイズの測定を試みた。ノイズ測定回路は繰り返し発生するノイズ波形を

サンプリングし、電源ノイズの波形を測定する回路である。

ノイズ測定回路を用いてデカップリング容量が電源ノイズに与える影響、

およびデカップリング容量の特性の測定を試みる。

また、基板電位を分離したMOSFETの基本特性測定回路を実装し、

基板電位を変化させた際のMOSFET特性を測定する。

測定結果から、電源ノイズ測定回路の動作を一部確認した。

また、基板電位を変化させることによりMOSFETの特性が変化することを

測定で確認し、基板電位とデバイス特性の基礎的なデータを得た。

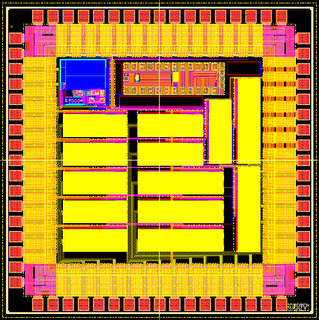

試作チップ4(0.35um)

無歪み伝送線路の特性を評価するためのテストチップ。UCSDのCK Cheng先生、京都大学土谷亮先生との共同研究です。

プロセス: 0.35um CMOS 3層アルミ配線プロセス

チップサイズ: 4.9mmX4.9mm

テープアウト: 2006年4月4日

設計者: Haikun Zhu(UCSD), CK CHeng(UCSD), 土谷先生(京大), 橋本

以下はVDEC年報2006の記事です。

チップ題目: シャントコンダクタンスを挿入したオンチップ伝送線路の特性評価 (RO3505_12)

チップ概要:

チップ内の通信性能向上の要求が高まっており,オンチップ伝送線

路を用いた高速信号伝送が有望視されている。本信号伝送では配線

の周波数依存特性による波形歪みや,シンボル間干渉によるジッタ

がスループットを低下させる要因となる.波形歪みを低減するため

に,シャントコンダクタンスを意図的に挿入した無歪み伝送線路が

提案されているが,実デバイスではまだ検証されていなかった。本

試作では無歪み伝送線路を搭載したテストチップを試作し,その特

性の実測を行った. 時間領域アイパターン測定,および周波数領域

Sパラメータ測定を行い,シャントコンダクタンスの有無,シャン

トコンダクタンスの値,および数が配線特性に与える影響を観測し

た. 特に,10Gbpsと高速な信号伝送を行った場合に,シャントコ

ンダクタンスを挿入した無歪み伝送線路において,シャントコン

ダクタンスを挿入していない通常の伝送線路と比較して,優れアイ

パターン特性が得られ,無歪み伝送線路の優位性を実デバイスで確

認した.さらに, シミュレーションによる予測結果と実測結果を比

較し, シミュレーションに用いた配線モデルの妥当性を明らかにした.

プロセス: 0.35um CMOS 3層アルミ配線プロセス

チップサイズ: 4.9mmX4.9mm

テープアウト: 2006年4月4日

設計者: Haikun Zhu(UCSD), CK CHeng(UCSD), 土谷先生(京大), 橋本

以下はVDEC年報2006の記事です。

チップ題目: シャントコンダクタンスを挿入したオンチップ伝送線路の特性評価 (RO3505_12)

チップ概要:

チップ内の通信性能向上の要求が高まっており,オンチップ伝送線

路を用いた高速信号伝送が有望視されている。本信号伝送では配線

の周波数依存特性による波形歪みや,シンボル間干渉によるジッタ

がスループットを低下させる要因となる.波形歪みを低減するため

に,シャントコンダクタンスを意図的に挿入した無歪み伝送線路が

提案されているが,実デバイスではまだ検証されていなかった。本

試作では無歪み伝送線路を搭載したテストチップを試作し,その特

性の実測を行った. 時間領域アイパターン測定,および周波数領域

Sパラメータ測定を行い,シャントコンダクタンスの有無,シャン

トコンダクタンスの値,および数が配線特性に与える影響を観測し

た. 特に,10Gbpsと高速な信号伝送を行った場合に,シャントコ

ンダクタンスを挿入した無歪み伝送線路において,シャントコン

ダクタンスを挿入していない通常の伝送線路と比較して,優れアイ

パターン特性が得られ,無歪み伝送線路の優位性を実デバイスで確

認した.さらに, シミュレーションによる予測結果と実測結果を比

較し, シミュレーションに用いた配線モデルの妥当性を明らかにした.

試作チップ3(90nm)

電源ノイズによる遅延変動評価回路。観測された遅延変動はシミュレーションと非常に良く一致しました。測定結果をIEEE Trans. on CAS-II, CICC2006で発表しました。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 130,000

ゲート数: 30,000

テープアウト日:2005/10/25

設計者: 小笠原君、橋本

VDEC年報2005の記事です。

チップ題目:電源ノイズ波形ならびに遅延変動測定 TEG (AS90054)

チップ概要:

本チップは電源・グラウンド線ノイズの波形, およびノイズによるゲート遅延の変動を測定することを目的とする. 1.5mm×1.0mm の領域にグリッド状の電源網を配線し,内部には動作の制御可能なノイズ発生回路を配置して、電源ノイズを発生させる.ノイズ発生回路は PLL で生成されるクロックを入力信号として動作し、動作するゲートの段数を制御することにより, ノイズの発生する時間を調節することができる.回路内に配置したリングオシレータの周期から, 電源ノイズによりゲート遅延が最大約 6 倍に増加する結果が得られた. さらに, PLL の動作周波数を上昇させると電源ノイズの影響が顕著となる傾向や, 電源ノイズの発生源から遠ざかるに従い,電源ノイズの影響が小さくなる傾向が観測された.また, 電源, グラウンド線の波形を外部から観測するため, 電源グリッドには 200 個のパッドを接続した. 引き続き測定を進める予定である。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 130,000

ゲート数: 30,000

テープアウト日:2005/10/25

設計者: 小笠原君、橋本

VDEC年報2005の記事です。

チップ題目:電源ノイズ波形ならびに遅延変動測定 TEG (AS90054)

チップ概要:

本チップは電源・グラウンド線ノイズの波形, およびノイズによるゲート遅延の変動を測定することを目的とする. 1.5mm×1.0mm の領域にグリッド状の電源網を配線し,内部には動作の制御可能なノイズ発生回路を配置して、電源ノイズを発生させる.ノイズ発生回路は PLL で生成されるクロックを入力信号として動作し、動作するゲートの段数を制御することにより, ノイズの発生する時間を調節することができる.回路内に配置したリングオシレータの周期から, 電源ノイズによりゲート遅延が最大約 6 倍に増加する結果が得られた. さらに, PLL の動作周波数を上昇させると電源ノイズの影響が顕著となる傾向や, 電源ノイズの発生源から遠ざかるに従い,電源ノイズの影響が小さくなる傾向が観測された.また, 電源, グラウンド線の波形を外部から観測するため, 電源グリッドには 200 個のパッドを接続した. 引き続き測定を進める予定である。

試作チップ2(90nm)

誘導性クロストークノイズによる遅延変動評価回路。試作チップ1の改良版。誘導性クロストークが明確に観測されました。測定結果をIEEE Journal of Solid-State Circuits, CICC2006で発表しました。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 25,000

ゲート数: 6,000

テープアウト日:2005/5/23

設計者: 小笠原君、橋本

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 25,000

ゲート数: 6,000

テープアウト日:2005/5/23

設計者: 小笠原君、橋本