Friday, December 08, 2006

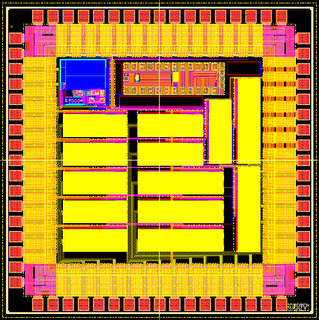

試作チップ5(90nm)

ダイナミック電源ノイズ波形測定。不具合があり目的を達せられず。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 400,000

ゲート数: 100,000

テープアウト日: 2006/7/14

設計者: 小笠原君、更田君、橋本

以下はVDEC年報2006の記事です。

チップ題目:電源ノイズ波形測定とMOS基板電位特性測定TEG (AS9006_2)

チップ概要:

本試作では電源ノイズによる電源電圧変動を測定する回路を実装し、

電源ノイズの測定を試みた。ノイズ測定回路は繰り返し発生するノイズ波形を

サンプリングし、電源ノイズの波形を測定する回路である。

ノイズ測定回路を用いてデカップリング容量が電源ノイズに与える影響、

およびデカップリング容量の特性の測定を試みる。

また、基板電位を分離したMOSFETの基本特性測定回路を実装し、

基板電位を変化させた際のMOSFET特性を測定する。

測定結果から、電源ノイズ測定回路の動作を一部確認した。

また、基板電位を変化させることによりMOSFETの特性が変化することを

測定で確認し、基板電位とデバイス特性の基礎的なデータを得た。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 400,000

ゲート数: 100,000

テープアウト日: 2006/7/14

設計者: 小笠原君、更田君、橋本

以下はVDEC年報2006の記事です。

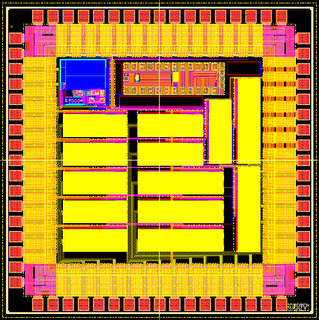

チップ題目:電源ノイズ波形測定とMOS基板電位特性測定TEG (AS9006_2)

チップ概要:

本試作では電源ノイズによる電源電圧変動を測定する回路を実装し、

電源ノイズの測定を試みた。ノイズ測定回路は繰り返し発生するノイズ波形を

サンプリングし、電源ノイズの波形を測定する回路である。

ノイズ測定回路を用いてデカップリング容量が電源ノイズに与える影響、

およびデカップリング容量の特性の測定を試みる。

また、基板電位を分離したMOSFETの基本特性測定回路を実装し、

基板電位を変化させた際のMOSFET特性を測定する。

測定結果から、電源ノイズ測定回路の動作を一部確認した。

また、基板電位を変化させることによりMOSFETの特性が変化することを

測定で確認し、基板電位とデバイス特性の基礎的なデータを得た。