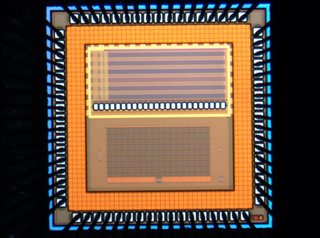

誘導性クロストークノイズによる遅延変動評価回路。試作チップ1の改良版。誘導性クロストークが明確に観測されました。測定結果をIEEE Journal of Solid-State Circuits, CICC2006で発表しました。

プロセス: 90nm CMOS6層銅配線プロセス

チップサイズ: 2.4x2.4mm

トランジスタ数: 25,000

ゲート数: 6,000

テープアウト日:2005/5/23

設計者: 小笠原君、橋本

# posted by Masanori Hashimoto @ 5:49 PM