Monday, January 29, 2007

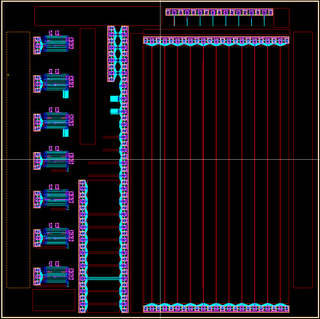

試作チップ9(0.35um)

無歪み伝送線路の特性を評価するためのテストチップの第2弾。UCSDのCK Cheng先生、京都大学土谷亮先生との共同研究です。電源ノイズ低減技術に関するテスト回路も搭載しています。

プロセス: 0.35um CMOS 3層アルミ配線プロセス

チップサイズ: 4.9mmX4.9mm

テープアウト: 2007年1月22日

設計者: 橋本

VDEC年報2007の記事です。

チップ題目: オンチップ伝送線路と電源ノイズ評価TEG

チップ概要:

本試作では波形歪みの小さいオンチップ伝送線路を搭載した。無歪み条件を部分的に満たすように、意図的に配線にシャントコンダクタンスを挿入し、伝送特性の周波数依存性を低下させる。本伝送線路の波形歪み低減効果を時間領域で評価するため、パターンジェネレータとオシロスコープを用いて、オンウェハプロービングでアイダイアグラムを測定する。別に、オンチップ電源ノイズ低減のため、デカップリング容量、ならびにスタブ伝送線路を付加した電源ノイズ発生回路を搭載した。消費電流の周波数成分の測定やアクティブプローブを用いた電源ノイズ波形を観測し、低減されるノイズの周波数成分を評価する。現在、いずれのテスト回路についても評価の準備を進めている。

[1] M. Hashimoto, J. Siriporn, A. Tsuchiya, H. Zhu, and C.-K. Cheng,

``Analytical Eye-Diagram Model for On-Chip Distortionless Transmission

Lines and Its Application to Design Space Exploration,'' Proc. CICC,

pp.869--872, 2007.

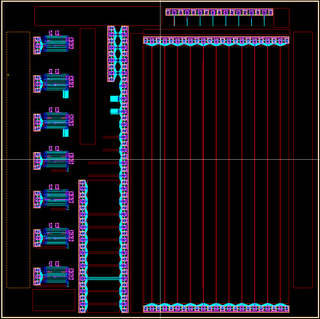

プロセス: 0.35um CMOS 3層アルミ配線プロセス

チップサイズ: 4.9mmX4.9mm

テープアウト: 2007年1月22日

設計者: 橋本

VDEC年報2007の記事です。

チップ題目: オンチップ伝送線路と電源ノイズ評価TEG

チップ概要:

本試作では波形歪みの小さいオンチップ伝送線路を搭載した。無歪み条件を部分的に満たすように、意図的に配線にシャントコンダクタンスを挿入し、伝送特性の周波数依存性を低下させる。本伝送線路の波形歪み低減効果を時間領域で評価するため、パターンジェネレータとオシロスコープを用いて、オンウェハプロービングでアイダイアグラムを測定する。別に、オンチップ電源ノイズ低減のため、デカップリング容量、ならびにスタブ伝送線路を付加した電源ノイズ発生回路を搭載した。消費電流の周波数成分の測定やアクティブプローブを用いた電源ノイズ波形を観測し、低減されるノイズの周波数成分を評価する。現在、いずれのテスト回路についても評価の準備を進めている。

[1] M. Hashimoto, J. Siriporn, A. Tsuchiya, H. Zhu, and C.-K. Cheng,

``Analytical Eye-Diagram Model for On-Chip Distortionless Transmission

Lines and Its Application to Design Space Exploration,'' Proc. CICC,

pp.869--872, 2007.